2018年11月软件设计师考试模拟题上午(一)之四

作者:wx6225b14cdec172023-12-24 01:00:13

备考咨询 刷题指导

添加专属学姐

摘要:对于【软件设计师】软考考试而言,试题无疑是最重要的学习资料之一。在软考备考过程中,吃透试题、掌握试题所考知识点、熟悉试题的出题思路,对我们提升分数的效果是最明显的,通过对试题的反复练习,还可以查漏补缺。今天,给大家带来【2018年11月软件设计师考试模拟题上午(一)】部分试题的详解,一起来看看吧~1、以下关于CISC(Complex Instruction Set Co

摘要:对于【软件设计师】软考考试而言,试题无疑是最重要的学习资料之一。在软考备考过程中,吃透试题、掌握试题所考知识点、熟悉试题的出题思路,对我们提升分数的效果是最明显的,通过对试题的反复练习,还可以查漏补缺。今天,给大家带来【2018年11月软件设计师考试模拟题上午(一)】部分试题的详解,一起来看看吧~

1、以下关于CISC(Complex Instruction Set Computer,复杂指令集计算机)和RISC(Reduced Instruction Set Computer,精简指令集计算机)的叙述中,错误的是( )。

A、 在CISC中,复杂指令都采用硬布线逻辑来执行

B、 一般而言,采用CISC技术的CPU,其芯片设计复杂度更高

C、 在RISC中,更适合采用硬布线逻辑执行指令

D、 采用RISC技术,指令系统中的指令种类和寻址方式更少

答案:A

答题解析:

2、以下关于Cache的叙述中,正确的是( )。

A、 在容量确定的情况下,替换算法的时间复杂度是影响Cache命中率的关键因素

B、 Cache的设计思想是在合理的成本下提高命中率

C、 Cache的设计目标是容量尽可能与主存容量相等

D、 CPU中的Cache容量应大于CPU之外的Cache容量

答案:B

答题解析:

3、挂接在总线上的多个部件,( )。

A、 只能分时向总线发送数据,并只能分时从总线接收数据

B、 只能分时向总线发送数据,但可同时从总线接收数据

C、 可同时向总线发送数据,并同时从总线接收数据

D、 可同时向总线发送数据,但只能分时从总线接收数据

答案:B

答题解析:

1、以下关于CISC(Complex Instruction Set Computer,复杂指令集计算机)和RISC(Reduced Instruction Set Computer,精简指令集计算机)的叙述中,错误的是( )。

A、 在CISC中,复杂指令都采用硬布线逻辑来执行

B、 一般而言,采用CISC技术的CPU,其芯片设计复杂度更高

C、 在RISC中,更适合采用硬布线逻辑执行指令

D、 采用RISC技术,指令系统中的指令种类和寻址方式更少

答案:A

答题解析:

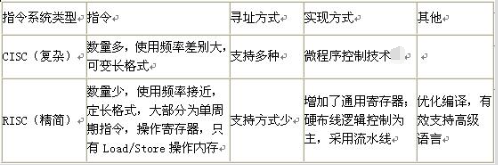

本题考查CISC与RISC的区别,这是一种常见的考题,二者的区别如表所示。

2、以下关于Cache的叙述中,正确的是( )。

A、 在容量确定的情况下,替换算法的时间复杂度是影响Cache命中率的关键因素

B、 Cache的设计思想是在合理的成本下提高命中率

C、 Cache的设计目标是容量尽可能与主存容量相等

D、 CPU中的Cache容量应大于CPU之外的Cache容量

答案:B

答题解析:

Cache是介于CPU与内存之间的一种高速缓存。这种存储器速度比内存快了很多倍,利用到局部性原理,只需要少量的Cache,便能使整个机器访问内存数据得到极大的提升。所以Cache是一种应用非常普遍的技术,Cache在实际应用中,可以分多级,如1级Cache,2级Cache。1级Cache往往位于CPU中,其容量比在主板上的2级Cache小,但速度比2级Cache快。

影响Cache命中率的因素包括高速存储器的容量、存储单元组的大小、组数多少、地址联想比较方法、替换算法、写操作处理方法和程序特性等,这些因素相互影响,没有关键影响因素。

3、挂接在总线上的多个部件,( )。

A、 只能分时向总线发送数据,并只能分时从总线接收数据

B、 只能分时向总线发送数据,但可同时从总线接收数据

C、 可同时向总线发送数据,并同时从总线接收数据

D、 可同时向总线发送数据,但只能分时从总线接收数据

答案:B

答题解析:

本题考查考生对总线概念的理解。总线是一个大家都能使用的数据传输通道,大家都可以使用这个通道,但发送数据时,是采用的分时机制,而接收数据时可以同时接收,也就是说,同一个数据,可以并行的被多个客户收取。如果该数据不是传给自己的,数据包将被丢弃。

查看完整试题>>>

软考资料: 2024年软考论文范文> 软考考试核心重点难点汇总> 查看更多>

备考刷题:章节练习+每日一练> 软考历年试题+模拟题>查看更多>